المقدمة

قيود الوقت هي بعض المعلومات ، والتي يمكن لأداة تحليل الوقت في نظام CAD أن تحسب ما إذا كانت البيانات ستمر بنجاح عبر جميع سجلات المشروع. يجب على المستخدم حساب هذه الحدود بنفسه وتدوينها في ملف الحدود الزمنية. بدون هذه القيود ، يكتب المستخدم مشروعًا بشكل عشوائي ، دون التحقق من أدائه ، وسوف يقسم المترجم أنه لم يجد أي قيود.

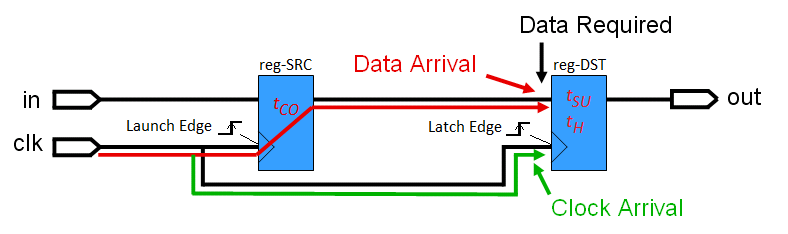

في المقال السابق ( link) تحدثت عن ماهية نقل البيانات بين سجلين وكيف يتم حساب تنفيذ علاقات التوقيت في حالة نقل البيانات داخل FPGA ، عندما يكون كلا المسجلين قيد الدراسة ، تقع مسارات إشارات الساعة وإشارات البيانات داخل FPGA. من هذه المقالة ، من الضروري استخلاص فهم مفهوم المنطق المتزامن كشبكة منسوجة من عدد كبير من عمليات النقل بين السجلات (الشكل 1) ، ومصطلح "الركود" (الشكل 2).

في هذه المقالة ، سننظر في حالات نقل البيانات ، التي يكون فيها أحد سجلي النقل خارج FPGA - هذا سجل لجهاز خارجي - متحكم دقيق ، ADC ، إلخ.

الشكل: 1. مخطط نقل البيانات بين التسجيلات من سجل المصدر (المصدر) إلى سجل الوجهة (الوجهة).

الشكل: 2. معنى الركود بالنسبة إلى مقدمة الالتقاط عند إدخال سجل الاستلام.

الصيغ العامة لحساب فترات الركود المشتقة في المادة السابقة:

دقيقةسهرشصسلأجك=دقيقةدأرأرهفشأناصهد-ماكسدأرأأصصأناالخامسأل=

=سر+دقيقةرجإلكرادستي-ماكسرجإلكراسرج-ماكسرسيو-ماكسرجا-ماكسرد

دقيقةحالدسلأجك=دقيقةدأرأأصصأناالخامسأل-ماكسدأرأرهفشأناصهد=

=-حر+دقيقةرجإلكراسرج-ماكسرجإلكرادستي+دقيقةرجا-ماكسرح+دقيقةرد

دعنا نراجع الشروط.

سلاك هو هامش من الوقت. يجب أن تكون إيجابية.

الوقت المحدد مسبقًا (وقت الإعداد ،رسيو) - الحد الأدنى من الوقت الذي يجب أن تكون فيه البيانات بالفعل عند إدخال سجل الاستلام في الوقت الذي تصل فيه مقدمة الساعة إلى إدخال ساعة جهاز الاستقبال.

تمسك بالوقترح) هو الحد الأدنى من الوقت الذي يجب أن تحتفظ فيه البيانات عند إدخال جهاز الاستقبال بعد وصول مقدمة الساعة إلى إدخال ساعة جهاز الاستقبال.

تسجيل وقت الاستجابة (ساعة إلى وقت الإخراج ،رجا) هو الوقت من وصول الساعة الأمامية إلى إدخال الساعة لسجل المصدر حتى ظهور بيانات مستقرة جديدة عند إخراجها.

SR و HR هما علاقة الإعداد والانتظار ، والفرق بين لحظات مقدمة الالتقاط وأمام الزناد عند مصدر الساعة ، مع مراعاة عدم الاستقرار. في حالة تحليل عمليات الإرسال FPGA الداخلية ، يتم أخذ الحواف الصاعدة للساعة فقط ، لذلك يتم تبسيط هذا التعبير إلىسر=تي-جسيو،حر=جحيو... لكن الواجهات غالبًا ما تستخدم جبهات مختلفة ، لذا يجب استخدام تمثيل أكثر عمومية.

تشويش الساعة المُعد مسبقًا / المستمر (CSU / CHU) هو مقياس لارتعاش الساعة. في العمليات الحسابية ، تحمل معنى هامش "فقط في حالة" لمراعاة الظواهر الناتجة عن التكرار غير الكامل للجلطة.

رد هو الوقت الذي تستغرقه إشارة البيانات للتنقل بين السجلات.

رجإلكراسرجهو الوقت الذي تستغرقه حافة إشارة الساعة للانتقال من مصدر الساعة إلى إدخال الساعة في سجل المصدر. ومن مصدر الساعة إلى الوجهة المسجلة - على التواليرجإلكرادستي...

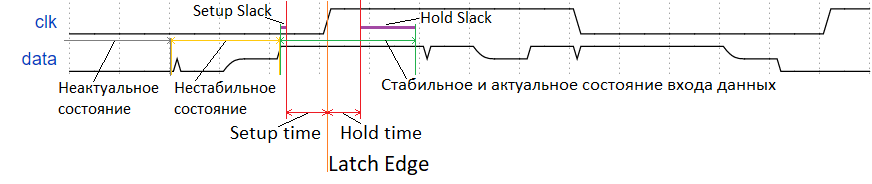

مسارات الإشارة موضحة في الشكل 3.

الشكل. 3. تحديد وقت السفر لمسارات إشارات وبيانات الساعة.

في هذه الصورة نرى نقطتين - خضراء وحمراء. كلاهما عبارة عن نقطتين لم تتباعد عندهما مسارات جزء المصدر والجزء الوجهة. النقطة الخضراء هي ناتج المخزن المؤقت العالمي للساعة ، وهو نقطة الدخول إلى شبكة الساعة العالمية لـ FPGA ، والتي تكون فيها مدخلات الساعة لجميع السجلات متساوية البعد تقريبًا. النقطة الحمراء هي نقطة اعتباطية في شبكة الساعة العالمية ، حيث ، كما هو الحال عند إدخال الشبكة ، لم تنقسم الساعة بعد إلى نسختين من نفسها ، والتي انتقلت إلى سجلات مختلفة. لكن النقطة الخضراء فقط هي النقطة المناسبة للبدء في حساب أوقات مرور الساعات ، لأنها في أحد الأماكن التي يفهمها المترجم. في هذا المثال ، عند إدخال شبكة الساعة العالمية. ولكن في حالة الواجهات البسيطة التي يتم تسجيلها من الخارج ، يمكن أن تكون النقطة الخضراء مجرد ساق FPGA.يعرف المترجم التوقيتات من هذه النقطة إلى كل من السجلات. والنقطة الحمراء ، مكان المصادفة العرضية لمساري الساعتين اللتين تم تحليلهما ، ليست مناسبة لنقطة البداية.

أنواع الإرسال التي تم تحليلها

دعونا نصنف الحالات للتحليل الزمني. يتم إجراء التحليل بشكل منفصل لكل جزء من FPGA فيما يتعلق بكتلة معينة. كنتيجة للتحليل ، يتم تقييم قدرة الساق على إرسال البيانات أو استقبالها بشكل صحيح. تتكون الواجهة الخارجية لتبادل البيانات المتزامن بين FPGA وجهاز خارجي من عدة خطوط متصلة بالأرجل. من بين هؤلاء ، خط واحد هو الخط الممزق. يجب أن يتم تقاسمها بين السجلات على كلا الجانبين. الخطوط المتبقية ، واحد أو أكثر ، هي خطوط إدخال أو إخراج أحادية الاتجاه. ما هو خط الإدخال لـ FPGA هو خط إخراج لجهاز خارجي ، والعكس صحيح. في هذه المقالة ، نأخذ في الاعتبار فقط أبسط حالات التحليل الزمني ، لذلك لا نتطرق إلى الواجهات غير المتزامنة وذاتية التوقيت ، وكذلك استخدام خطوط الإدخال / الإخراج ثنائية الاتجاه.

يمكن تصنيف حالات التحليل وفقًا لاتجاه البيانات بالنسبة إلى FPGA (الإدخال / الإخراج) واتجاه الساعة بالنسبة إلى FPGA (يتم تسجيل البيانات من FPGA / من مصدر خارجي). لكل حالة ، هناك نوعان من التحليل (الإعداد / الانتظار). إجمالاً ، أربع حالات للتحليل وثماني معادلات نحتاج إلى اشتقاقها.

إخراج البيانات المسجلة بواسطة ساعة FPGA داخلية

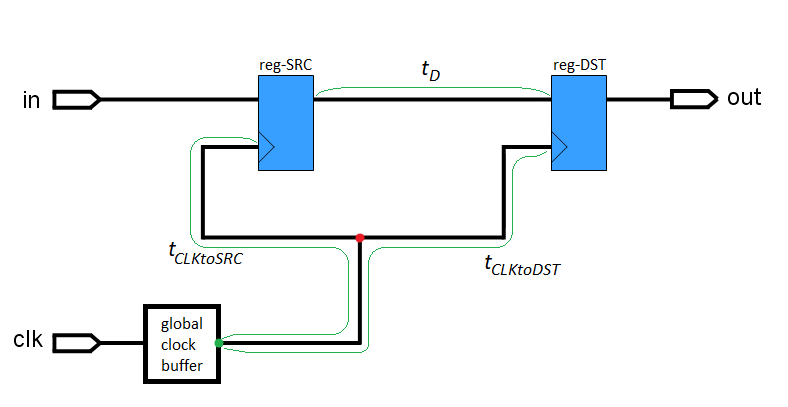

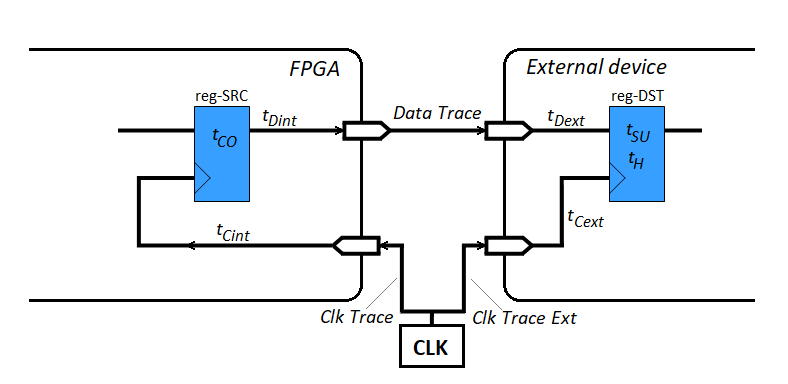

ضع في اعتبارك الحالة عندما نحتاج إلى إعطاء شيء ما على كفتنا (الشكل 4).

مخطط نقل البيانات الأساسي لم يتغير. لكن السجلات تنتمي الآن إلى دائرتين صغيرتين مختلفتين ، ومسار البيانات بينهما ليس منطقًا توليفيًا ، ولكنه مجرد مسارات على السبورة. ومهمتنا هي تكييف صيغ سلاك المعروفة مع موقف مختلف قليلاً.

الشكل: 4. نقل البيانات إلى الخارج على ساعة FPGA الخاصة بك.

في الشكل 4 ، نرى مخطط تحويل بين السجلات. يعرض أوقات العمليات المرتبطة بكل من السجلات ، والأوقات التي تنتقل فيها الإشارات عبر المسارات.

لقد قمت بتعيين الفهرسة التالية: يتم تمييز الوقت المرتبط بالبيانات بالحرف D. يتم تمييز الوقت المرتبط بالساعة بالحرف C. إذا حدث حدث داخل FPGA ، فسيتم تمييز وقته بفهرس "int" ، وإذا كان في جهاز خارجي ، فسيتم تمييز وقته "ext" ... يحتوي الوقت الذي تستغرقه القطعة للانتقال من مصدر القطعة إلى جذع خروج القطعة على أطول مؤشر "Cintout". DataTrace و ClkTrace هي أوقات السفر للآثار المقابلة على ثنائي الفينيل متعدد الكلور. كتلة "CLK" ترمز إلى نوع من المصدر الداخلي للساعات.

السمة الرئيسية للكميات المذكورة في الشكل أنها كلها موجبة. كل منهم يساوي المدة المطلقة لأي عمليات فيزيائية ، مما يعني أنها جسديًا يمكن أن تكون قيمًا موجبة فقط. هذا مهم لمزيد من التفكير.

الآن سوف نلقي نظرة فاحصة على تحليل فترة السماح المحددة مسبقًا. بالنظر إلى الشكل 4 ، يمكننا بسهولة ربط القيم المرصودة بشروط معادلات الركود:

الآن دعنا نستبدل هذه المساواة في صيغة فترة السماح المحددة مسبقًا:رجإلكراسرج=رجأنانر

رد=ردأنانر+دأرأتيصأجه+ردهxر

رجإلكرادستي=رجأنانراشر+جلكتيصأجه+رجهxر

دقيقةسهرشصسلأجك=دقيقةدأرأرهفشأناصهد-ماكسدأرأأصصأناالخامسأل=

=سر+دقيقةرجإلكرادستي-ماكسرجإلكراسرج-ماكسرسيو-ماكسرجا-ماكسرد=

=سر+دقيقة(رجأنانراشر+جلكتيصأجه+رجهxر)-ماكس(رجأنانر)-رسيو-رجا-

-ماكس(ردأنانر+دأرأتيصأجه+ردهxر)

نستخدم الآن معرفة أن جميع الحدود بين الأقواس أكبر من صفر. لذلك نحن نعرف كيفية فتح هذه الأقواس: الحد الأدنى للمبلغ يساوي مجموع القيم الدنيا ، والحد الأقصى للمبلغ يساوي مجموع الحد الأقصى:

دقيقةسهرشصسلأجك=سر+دقيقةرجأنانراشر+دقيقةجلكتيصأجه+دقيقةرجهxر-ماكسرجأنانر-

-رسيو-رجا-ماكسردأنانر-ماكسدأرأتيصأجه-ماكسردهxر

الآن دعونا نعيد ترتيب المصطلحات في الأماكن لتجميع شروط العمليات داخل FPGA والعمليات داخل الجهاز الخارجي بين قوسين:

دقيقةسهرشصسلأجك=سر-(ماكسرجأنانر+رجا+ماكسردأنانر-دقيقةرجأنانراشر)+

+دقيقةجلكتيصأجه-ماكسدأرأتيصأجه-(ماكسردهxر+رسيو-دقيقةرجهxر)

ماذا نرى بين قوسين؟ إذا نظرت عن كثب وتذكرت مرة أخرى أن جميع القيم المشار إليها أكبر من الصفر ، فيمكننا القول إننا نرى تعبيرًا عن وقت استجابة مكافئ معين (بعلامة النجمة) لسجل FPGA ووقت الضبط المسبق المكافئ لسجل الجهاز الخارجي:

ماكسرجأنانر+رجا+ماكسردأنانر-دقيقةرجأنانراشر=ماكسر∗جا

ماكسردهxر+رسيو-دقيقةرجهxر=ماكسر∗سيو

دقيقةسهرشصسلأجك=سر-ماكسر∗جا+دقيقةجلكتيصأجه-ماكسدأرأتيصأجه-ماكسر∗سيو

لماذا لا نستخدم قيمًا متكافئة إذا كان صانعو الشرائح قد قاموا بالفعل بحسابها لنا بناءً على تأخيراتهم الداخلية؟ سيتم حساب القيم المكافئة على جانب FPGA بواسطة المترجم دون تدخل المستخدم ، ويتم الإشارة صراحة إلى القيم المكافئة للجهاز الخارجي في ورقة البيانات الخاصة بالجهاز.

الآن دعنا نلقي نظرة فاحصة على التعبير الأخير. في ذلك ، فإن المصطلحات الثلاثة الأولى معروفة بالفعل للمحلل ، لأننا أوضحنا لها بالفعل تردد التشغيل وحجم عدم الاستقرار. تم تتبع المترجم والمحلل يعرف وقت الاستجابة المكافئ لسجله. هذا يعني أن المحلل يعرف مدة جميع العمليات داخل FPGA. لكن المصطلحات الثلاثة الأخيرة فريدة لكل ساق ويحتاج المستخدم إلى حسابها بنفسه والإشارة إلى المحلل كرقم. ما هذا الرقم؟ بإلقاء نظرة فاحصة على المصطلحات الثلاثة الأخيرة ، سنرى أنه يمكن تفسيرها على أنها حد أقصى سالب لقيمة معينة:

دقيقةجلكتيصأجه-ماكسدأرأتيصأجه-ماكسر∗سيو=-ماكساشرصشردهلأذ

وهذه القيمة مساوية بشكل مفيد لتأخير كل شيء يحدث خارج FPGA ، بالنسبة إلى كل ما يحدث في الداخل. يطلق عليه ذلك - تأخير الإخراج ، تأخير الإخراج.

دعونا نلخص:

دقيقةسهرشصسلأجك=سر-ماكسر∗جا-ماكساشرصشردهلأذ

ماكساشرصشردهلأذ=ماكسدأرأتيصأجه+ماكسر∗سيو-دقيقةجلكتيصأجه=

=ماكس(دأرأتيصأجه+ر∗سيو-جلكتيصأجه)

سنشتق الآن معادلة مماثلة لفترة السماح. تذكر المعادلة العامة واستبدلها بالمصطلحات الجديدة:

لنفتح الأقواس ونجمع المصطلحات على الفور حول كل من السجلات:دقيقةحالدسلأجك=دقيقةدأرأأصصأناالخامسأل-ماكسدأرأرهفشأناصهد=

=-حر+دقيقةرجإلكراسرج-ماكسرجإلكرادستي+دقيقةرجا-ماكسرح+دقيقةرد=

=-حر+دقيقة(رجأنانر)-ماكس(رجأنانراشر+جلكتيصأجه+رجهxر)+رجا-رح+

+دقيقة(ردأنانر+دأرأتيصأجه+ردهxر)

ومرة أخرى نرى كيف جمعت الحدود في كميات متساوية ، هذه المرة رجا و رح:دقيقةحالدسلأجك=-حر+(رجا+دقيقةرجأنانر+دقيقةردأنانر-ماكسرجأنانراشر)-

-ماكسجلكتيصأجه+دقيقةدأرأتيصأجه-(رح-دقيقةردهxر+ماكسرجهxر)

ويمكن فهم المصطلحات الثلاثة الأخيرة على أنها الحد الأدنى من التأخير الخارجي:دقيقةحالدسلأجك=-حر+دقيقةر∗جا+دقيقةدأرأتيصأجه-ماكسجلكتيصأجه-ماكسر∗ح

دقيقةدأرأتيصأجه-ماكسجلكتيصأجه-ماكسر∗ح=دقيقةاشرصشردهلأذ

دعونا نلخص:

دقيقةحالدسلأجك=-حر+دقيقةر∗جا+دقيقةاشرصشردهلأذ

دقيقةاشرصشردهلأذ=دقيقة(دأرأتيصأجه-جلكتيصأجه-ر∗ح)

يجب التأكيد على ذلك دقيقةاشرصشردهلأذ و ماكساشرصشردهلأذ- هذا هو الحد الأدنى والحد الأقصى وليس نفس القيمة على الإطلاق. يأخذ كل تحليل محدد مسبقًا وتحليل استبقاء بعين الاعتبار مواقف مختلفة وتأخيرات خارجية مختلفة. هذا يعني أن المصطلحات ، كما يتضح من الصيغ ، مأخوذة بشكل مختلف.

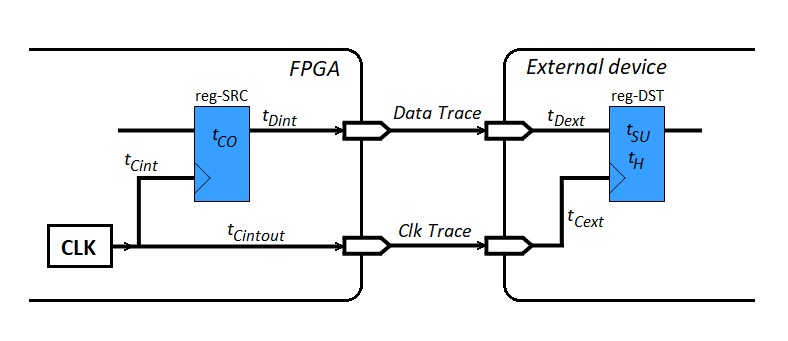

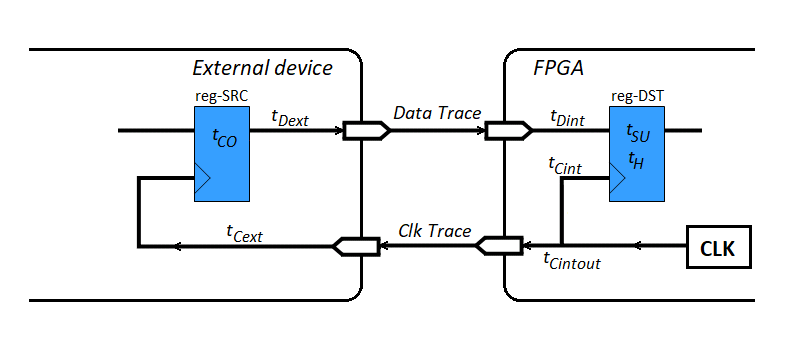

إخراج البيانات بساعة خارجية

الآن دعنا ننتقل إلى الحالة عندما نحتاج إلى إعطاء شيء ما للخارج ، ولكن وفقًا لساعة خارجية لـ FPGA (الشكل 5). بشكل عام ، يقع مصدر الساعة خارج FPGA ، على وجه الخصوص ، يمكن أن يكون داخل جهاز خارجي.

الشكل: 5. نقل البيانات إلى الخارج عبر ساعة خارجية.

في الشكل 5 ، نرى مصدر التقطيع بالخارج. تبعا لذلك ، الكميةرجأنانراشروظهر وقت مرور القطعة إلى الجهاز الخارجي "Clk Trace Ext".

بالنظر إلى الشكل 5 ، نربط القيم المرصودة بشروط معادلات الركود العامة:

رجإلكراسرج=جلكتيصأجه+رجأنانر

رد=ردأنانر+دأرأتيصأجه+ردهxر

رجإلكرادستي=جلكتيصأجههxر+رجهxر

باستخدام هذه التعبيرات ، نفتح المصطلحات في صيغة فترة السماح المحددة مسبقًا ، ونجمعها على الفور حسب السجلات ونحصل على الشكل المكافئ:

دقيقةسهرشصسلأجك=دقيقةدأرأرهفشأناصهد-ماكسدأرأأصصأناالخامسأل=

=سر+دقيقةرجإلكرادستي-ماكسرجإلكراسرج-ماكسرسيو-ماكسرجا-ماكسرد=

=سر-(ماكسرجأنانر+رجا+ماكسردأنانر)-ماكسدأرأتيصأجه-

-(ماكسردهxر+رسيو-دقيقةرجهxر)-ماكسجلكتيصأجه+دقيقةجلكتيصأجههxر=

=سر-ماكسر∗جا-ماكس(ر∗سيو+دأرأتيصأجه+جلكتيصأجه-جلكتيصأجههxر)

دقيقةسهرشصسلأجك=سر-ماكسر∗جا-ماكساشرصشردهلأذ

ماكساشرصشردهلأذ=ماكس(ر∗سيو+دأرأتيصأجه+جلكتيصأجه-جلكتيصأجههxر)

نقوم بتحليل فترة السماح بالاحتفاظ بنفس الطريقة:

دقيقةحالدسلأجك=دقيقةدأرأأصصأناالخامسأل-ماكسدأرأرهفشأناصهد=

=-حر+دقيقةرجإلكراسرج-ماكسرجإلكرادستي+دقيقةرجا-ماكسرح+دقيقةرد=

=-حر+(دقيقةرجأنانر+رجا+دقيقةردأنانر)+دقيقةدأرأتيصأجه+دقيقةجلكتيصأجه-

-(رح-دقيقةردهxر+ماكسرجهxر)-ماكسجلكتيصأجههxر=

=-حر+دقيقةر∗جا+دقيقةدأرأتيصأجه+دقيقةجلكتيصأجه-ماكسجلكتيصأجههxر-ماكسر∗ح

دقيقةحالدسلأجك=-حر+دقيقةر∗جا+دقيقةاشرصشردهلأذ

دقيقةاشرصشردهلأذ=دقيقة(دأرأتيصأجه+جلكتيصأجه-جلكتيصأجههxر-ر∗ح)

إذا اعتبرنا في هذا المخطط حالة معينة (لكن متكررة) ، عندما يكون مصدر الخدعة داخل جهاز خارجي ، فإن الصيغ المشتقة ستتغير فقط من خلال حقيقة أن ClkTraceExt يصبح مساويًا للصفر فيها. سيؤدي نقل مصدر الساعة داخل الجهاز الخارجي في حساباتنا إلى انتشار مجهري للجلطة داخل الجهاز الخارجي بين إخراج الساعة والسجل ، ولكن سيتم أخذ ذلك في الاعتبار من قبل الشركة المصنعة للجهاز الخارجي وسيتم تضمينه في القيم المكافئةر∗سيو و ر∗ح...

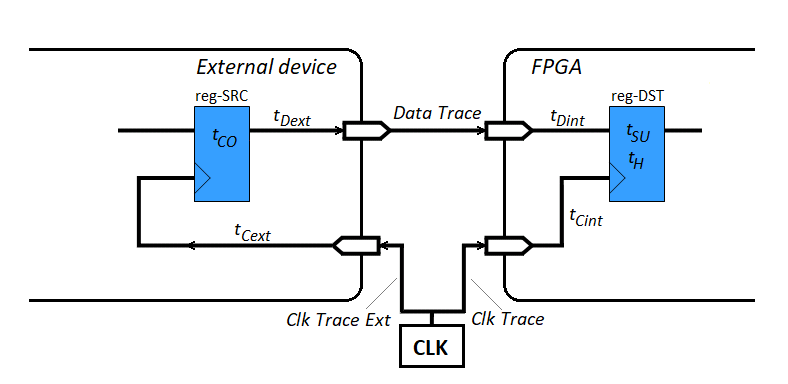

إدخال البيانات المسجلة بواسطة ساعة FPGA داخلية

ننتقل الآن إلى النظر في أرجل الإدخال للواجهة المتزامنة. يتم تبديل FPGA والجهاز الخارجي في الشكل 6.

الشكل: 6. استقبال البيانات على ساعة FPGA الخاصة بك.

تحليل مثل هذا المخطط ليس أكثر تعقيدًا من السابق.

نكشف ، نجمع ...رجإلكراسرج=رجأنانراشر+جلكتيصأجه+رجهxر

رد=ردهxر+دأرأتيصأجه+ردأنانر

رجإلكرادستي=رجأنانر

ونحصل على قيمة التأخير الخارجي ، والتي سنطلق عليها هذه المرة الإدخال:دقيقةسهرشصسلأجك=دقيقةدأرأرهفشأناصهد-ماكسدأرأأصصأناالخامسأل=

=سر+دقيقةرجإلكرادستي-ماكسرجإلكراسرج-ماكسرسيو-ماكسرجا-ماكسرد=

=سر-(رسيو+ماكسردأنانر-دقيقةرجأنانر+ماكسرجأنانراشر)-ماكسدأرأتيصأجه-

-(رجا+ماكسردهxر+ماكسرجهxر)-ماكسجلكتيصأجه

دقيقةسهرشصسلأجك=سر-ماكسر∗سيو-ماكسأنانصشردهلأذ

ماكسأنانصشردهلأذ=ماكس(دأرأتيصأجه+ر∗جا+جلكتيصأجه)

الآن فترة الانتظار:

دقيقةحالدسلأجك=دقيقةدأرأأصصأناالخامسأل-ماكسدأرأرهفشأناصهد=

=-حر+دقيقةرجإلكراسرج-ماكسرجإلكرادستي+دقيقةرجا-ماكسرح+دقيقةرد=

=-حر-(رح-دقيقةردأنانر+ماكسرجأنانر-دقيقةرجأنانراشر)+دقيقةدأرأتيصأجه+

+(رجا+دقيقةردهxر+دقيقةرجهxر)+دقيقةجلكتيصأجه

دقيقةحالدسلأجك=حر-ماكسر∗ح+دقيقةأنانصشردهلأذ

دقيقةأنانصشردهلأذ=دقيقة(ر∗جا+دأرأتيصأجه+جلكتيصأجه)

إدخال البيانات بساعة خارجية

أيضًا ، وفقًا للمخرش ، ننظر إلى مخطط نقل البيانات ونكشف عن شروط الصيغة العامة.

الشكل: 7. استقبال البيانات على الساعات الخارجية.

رجإلكراسرج=جلكتيصأجههxر+رجهxر

رد=ردهxر+دأرأتيصأجه+ردأنانر

رجإلكرادستي=جلكتيصأجه+رجأنانر

صيغة الركود المحددة مسبقًا:

دقيقةسهرشصسلأجك=دقيقةدأرأرهفشأناصهد-ماكسدأرأأصصأناالخامسأل=

=سر+دقيقةرجإلكرادستي-ماكسرجإلكراسرج-ماكسرسيو-ماكسرجا-ماكسرد=

=سر-(رسيو+ماكسردأنانر-دقيقةرجأنانر)-ماكسدأرأتيصأجه-

-(رجا+ماكسردهxر+ماكسرجهxر)-ماكسجلكتيصأجههxر+دقيقةجلكتيصأجه=

=سر-ماكسر∗سيو-ماكس(ر∗جا+دأرأتيصأجه+جلكتيصأجههxر-جلكتيصأجه)

دقيقةسهرشصسلأجك=سر-ماكسر∗سيو-ماكسأنانصشردهلأذ

ماكسأنانصشردهلأذ=ماكس(ر∗جا+دأرأتيصأجه+جلكتيصأجههxر-جلكتيصأجه)

صيغة الاحتفاظ بفترة السماح:

دقيقةحالدسلأجك=دقيقةدأرأأصصأناالخامسأل-ماكسدأرأرهفشأناصهد=

=-حر+دقيقةرجإلكراسرج-ماكسرجإلكرادستي+دقيقةرجا-ماكسرح+دقيقةرد=

=-حر-(رح-دقيقةردأنانر+ماكسرجأنانر)+دقيقةدأرأتيصأجه+

+(رجا+دقيقةردهxر+دقيقةرجهxر)+دقيقةجلكتيصأجههxر-ماكسجلكتيصأجه

دقيقةحالدسلأجك=-حر-ماكسر∗ح+دقيقةأنانصشردهلأذ

دقيقةأنانصشردهلأذ=دقيقة(ر∗جا+دأرأتيصأجه+جلكتيصأجههxر-جلكتيصأجه)

مرة أخرى ، إذا كان مصدر الساعة داخل جهاز خارجي ، فقم ببساطة بمساواة ClkTraceExt بالصفر.

تفسير بصري

الصيغ جيدة بالتأكيد ، ولكن إذا تعمقت في هذا الموضوع لأول مرة ، فإن الصيغ تبدو غير مفهومة وغير حية. أريد شيئًا أكثر وضوحًا حتى تكتسب الصيغ معنى مرئيًا. حسنًا ، دعنا نحلل المعنى المادي للصيغ ، على سبيل المثال ، حالة إخراج البيانات بواسطة ساعة خارجية . دعني أذكرك كيف يبدو الرسم التخطيطي والصيغ:

الشكل. 8. نقل البيانات للخارج عبر ساعة خارجية.

دقيقةسهرشصسلأجك=دقيقةدأرأرهفشأناصهد-ماكسدأرأأصصأناالخامسأل=

=سر-ماكسر∗جا-ماكسر∗سيو-ماكسدأرأتيصأجه-ماكسجلكتيصأجه+دقيقةجلكتيصأجههxر

دقيقةحالدسلأجك=دقيقةدأرأأصصأناالخامسأل-ماكسدأرأرهفشأناصهد=

=-حر+دقيقةر∗جا+دقيقةدأرأتيصأجه+دقيقةجلكتيصأجه-ماكسجلكتيصأجههxر-ماكسر∗ح

أثناء نقل البيانات ، يحدث حدثان: حرائق سجل المصدر وحرائق سجل الوجهة. تحدث الأحداث لأنها تنطلق من جبهات clok الخارجة من مصدر الكتلة. من هنا سنبدأ في البحث.

يولد مصدر الساعة واجهة بدء التشغيل ويصل إلى FPGA أثناء ClkTrace. بعد ذلك ، يتم تشغيل سجل FPGA أثناءر∗جا... علاوة على ذلك ، تنتقل البيانات الجديدة التي تم إنشاؤها بواسطة هذا المشغل من FPGA إلى الجهاز الخارجي أثناء DataTrace.

من ناحية أخرى ، يُنشئ مصدر الساعة أيضًا لقطة أمامية تصل إلى الجهاز الخارجي أثناء ClkTraceExt.

يقع هذان الحدثان عند إدخال البيانات لجهاز خارجي. وهنا من المهم أن تصل البيانات هناك قبل أن يبدأ سجل الاستلام في الالتقاط. يجب أن يأتوا مع بقاء بعض الوقت على الأقل.ر∗سيو، أو الأفضل من ذلك. تعتبر أسوأ حالة لضمان صحة ذلك. إذا كان هناك مخزون ، حتى في أسوأ الحالات ، فكل شيء في محله بالتأكيد. لذلك فإن أسوأ لحظة لوصول البيانات هي اللحظة الأخيرة ،ماكس(جلكتيصأجه+ر∗جا+دأرأتيصأجه)... وأسوأ لحظة في انتظار البيانات هي اللحظة الأولى ،دقيقةجلكتيصأجههxر-ماكسر∗سيو... وحتى في أسوأ الحالات ، يجب أن تكون اللحظة الثانية بعد الأولى:

نأمل أن يلقي هذا التفسير مزيدًا من الضوء على ما يحدث.إلأرجحهدزه+دقيقةجلكتيصأجههxر-ماكسر∗سيو>

>إلأشنجحهدزه+ماكس(جلكتيصأجه+ر∗جا+دأرأتيصأجه)

في هذا التعبير ، نرى لحظات الجبهات - LaunchEdge و LatchEdge ، والتي عادة ما تكون مخفية في مصطلحات SR و HR. دعونا نتذكر ما هو عليه. يتم

أخذ أربعة حواف في الاعتبار في تحليل الإعداد المسبق والاحتفاظ: إعداد Launch Edge - الحافة التي ستجعل المصدر يرسل البيانات التي يجب على جهاز الاستقبال التقاطها.

يعد Hold Launch Edge هو الواجهة التي ستجبر المصدر على إرسال البيانات التالية ، مما قد يمنع المستلم من الحصول على البيانات السابقة. بحكم التعريف ، هناك دائمًا فترة ساعة واحدة بين Setup LaunchEdge و Hold Launch Edge.

Setup Latch Edge هي الواجهة التي ستجبر جهاز الاستقبال على التقاط بيانات الإدخال.

Hold Latch Edge هو نفس Setup Latch Edge. وهذا يعني ، في الواقع ، أن Latch Edge هي واحدة ماديًا ، فهي ببساطة تُعطى اسمين للجمال في نوعين من التحليل.

داخل FPGAs ، عادةً ما يعمل المنطق المتزامن فقط على الحواف الصاعدة (الشكل 9). في هذه الحالة ، من وجهة نظر تحليل فترة السماح ، يتم تباعد الإعدادات المسبقة لـ Setup Launch Edge و Setup Latch Edge عن بعضها البعض بفترة ساعة واحدة ، ومن وجهة نظر تحليل الإمساك ، يتزامن Hold Launch Edge و Hold Latch Edge.

الشكل: 9. الترتيب المتبادل للحواف في الحالة عندما يتم تسجيل كلا السجلين بالحواف الصاعدة.

ومع ذلك ، لا أحد يحظر وضع إشارة الساعة المقلوبة على مدخل الساعة لأحد السجلين ، وبالتالي يجعلها تعمل على الحافة الساقطة للساعة. بالمناسبة ، يتم ذلك غالبًا في نفس واجهات SPI. دعنا نلقي نظرة فاحصة على هذا الخيار.

دعونا نفكر في حالة إخراج البيانات من FPGA بواسطة ساعة خارجية ، لكن أحد السجلين يعمل على ساعة مقلوبة ، أي على طول حافة هبوط. فليكن تسجيل استلام على جهاز خارجي. ثم يتم توزيع أدوار الجبهات في الوقت المناسب بشكل مختلف (الشكل 10).

الشكل: 10. الترتيب المتبادل للجبهات في الحالة عندما يكون المصدر مسجلاً بالحافة الصاعدة ، والمتلقي بالحافة المتساقطة.

يتيح لك تضمين السجلات هذا محاذاة حجم فترات الركود للإعداد المسبق والانتظار. إذا كانت السجلات تعمل من جبهات نفس الاتجاه ، فبسبب ضآلة انتشار الإشارات على طول مسارات اللوحة ، مقارنةً بفترة الساعة ، فإن فترة السماح المحددة مسبقًا ستكون ضخمة ، وسيكون فترة الانتظار صغيرة جدًا.

يوضح الشكل 11 توقيت الساعة عند مصدر الساعة. لتبسيط الشكل ، لم أحدد مصطلح ClkTraceExt. سنفترض أن مصدر التقطيع موجود داخل جهاز خارجي.

الشكل: 11. موضع فترات الركود في الوقت المناسب بالنسبة إلى واجهات الساعات في الحالة عندما يتم تسجيل جهاز الاستقبال من خلال حافة السقوط.

في هذه الصورة ، الحد الأقصى لوصول البيانات- هذه هي آخر لحظة يمكن أن تصل فيها البيانات إلى مدخلات جهاز الاستقبال. أول لحظة يجب أن تكون فيها البيانات بالفعل عند إدخال جهاز الاستقبال هي min Data Required . آخر لحظة عندما لا تزال البيانات بحاجة إلى إدخالها هي الحد الأقصى للبيانات المطلوبة . وتسمى اللحظة الأولى التي يمكن فيها للبيانات أن تترك مدخلات المستلم بالفعل ، مع استبدالها بالبيانات التالية ، مين ترك البيانات .

الآن يجب أن تصبح الصيغ وشروطها أكثر وضوحًا.

كيفية استخدام الصيغ الناتجة

لقد حصلنا على صيغ للتأخيرات الخارجية ويمكننا حساب عدد محدد من التأخيرات لملاءمتها في ملف قيود الوقت. على الصعيد العالمي ، تتكون هذه الصيغ من نوعين من المصطلحات - خصائص التوقيت لمنافذ الجهاز الخارجي والكمون على مسارات اللوحة.

عادة ما توجد مواصفات المنفذ في أوراق البيانات تحت أقسام بعنوان "الخصائص الكهربائية / مواصفات التيار المتردد / متطلبات التوقيت". في بعض الأحيان يتم استدعاء هذه الخصائص بأسماء مختلفة وعليك أن تكون ذكيًا للعثور عليها. لكن الجداول التي تحتوي على أرقام عادة ما تكون مصحوبة بمخططات توقيت تسمح لك بتحديد المعلمة التي تريدها. فارق بسيط مهم ، يمكن أن يكون مربكًا ، في أوراق البيانات للعديد من الدوائر المصغرة ، غالبًا ما يتم وصف دبابيس الإخراج بواسطة معلمات "وقت إخراج الإعداد" و "وقت الانتظار للإخراج". في صيغ هذه المقالة ، ينبغي مقارنتها على النحو التالي:رسيوا=ماكسر∗جا،رحا=دقيقةر∗جا...

مع المسارات ، الأمر أكثر تعقيدًا بعض الشيء. الحساب الدقيق للكمون على السبورة ليس سؤالا تافها. يعتمد التأخير على طول المسار وعرضه وسمكه وزواياه ، وسمك ومادة اللوحة ، والمسافة إلى طبقات الأرض المختلفة ، وقرب المسارات من بعضها البعض ، والعديد من العوامل الأخرى. ومع ذلك ، فإن تأثير كل من هذه العوامل صغير نوعًا ما ويمكن إهمال هذه الصعوبات عند ترددات واجهة منخفضة تصل إلى عشرات الميجاهرتز. يبدو الحساب المبسط لتأخر المسار على النحو التالي: تُعتبر سرعة انتشار الموجة في الرقاقة مساوية لنصف سرعة الضوء في الفراغ. بعد التحويل ، يعطي هذا حوالي 0.007 نانوثانية / مم. يتم تعويض الخطأ في هذا التقدير من خلال مجموعة واسعة من تقديرات التأخير. للحصول على أقصى تأخير ، نعتبر التأخير المحدد يساوي 0.010 نانوثانية / مم ، وللحد الأدنى - 0.005 نانوثانية / مم.

هناك فارق بسيط آخر. يحاول مهندسو الدوائر ، عند تصميم لوحات الدوائر المطبوعة ، تمديد مسارات الواجهات المتزامنة بنفس الطريقة تقريبًا والحفاظ على أطوالها المتساوية. تحقق من البيانات وأطوال مسار الساعة على السبورة المستهدفة. على الأرجح أنها متساوية تقريبًا ويمكن اعتبار مكون التعبيرات (DataTrace - ClkTrace) عمليًا فارغًا.

إذا كان هناك عنصر تأخير في مسار البيانات أو القطعة ، فيجب أيضًا أخذه في الاعتبار. يمكن أن يكون مخزنًا مؤقتًا أو عاكسًا أو محول مستوى أو عزلًا كلفانيًا. هذه العناصر قادرة على إحداث تأخير كبير جدًا ، عشرات النانو ثانية ، لذلك يجب معالجتها بعناية فائقة.

خاتمة

في هذه المقالة ، شاهدت الصيغ التي تحدد تنفيذ قيود الوقت في الواجهات المتزامنة. بمعرفة هذه الصيغ ، يمكنك فهم ما يعتمد عليه نقل البيانات الناجح وكيفية حساب الحدود الصحيحة للمحلل. في المقالة التالية سأقدم مثالاً على تنسيق ملف قيود الوقت واستخدام المحلل.