ومع ذلك ، قد يكون استخدام DAC / ADC أو تصحيحه أمرًا صعبًا بسبب القيود التي تضعها الشركة المصنعة للجهاز ، على سبيل المثال ، على البرنامج المستخدم أو كيفية التحكم في الجهاز. هذا يقترح تصميم نموذج التفاعل الخاص بك.

في هذه المقالة سننظر في إمكانية تنظيم التفاعل بين جهاز كمبيوتر و DAC / ADC باستخدام FPGAs.

مقدمة

الغرض الرئيسي من هذه المقالة هو وصف الحل لمشكلة معينة ، وكذلك الإلمام بواجهات تفاعل الدوائر المتكاملة (IC). الغرض الرئيسي من DAC / ADC لا يعتبر هنا.

تتطلب هذه المقالة بعض المعرفة بالبرمجة والدوائر الموجهة للكائنات ، لذلك إذا لم تكن معتادًا على هذه المفاهيم ، فمن المستحسن أن تبدأ بها.

آمل أن تكون تجربة الشخص الذي يواجه مشكلة اتصال الأجهزة الإلكترونية لأول مرة مفيدة لشخص ما.

حظا سعيدا وإنجازات جديدة للجميع!

برنامج تعليمي صغير على الواجهات

تنصل

إذا كنت معتادًا على بنية الواجهات الرئيسية المستخدمة لاتصالات IC ، فيمكنك تخطي هذه النقطة بأمان.

برنامج تعليمي

, .

, (, .) . , .

, . , , , .. , . . – , . , . , .

, .

( ), :

«-» — , . , — .

«» (, « » «») , . . , , , . .

( «») . , , , - . .

:

, . . . , .

, . , , .

(-/)

:

. .

, .

: , «» .

. .

:

. . . ( – , – , , ). « » ( ). .

, , .

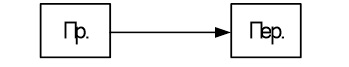

() SPI I2C UART.

I2C – . I2C . I2C «-», .

, , . , . 7- 16 . , 112 . I2C (SDA) (SCL).

I2C

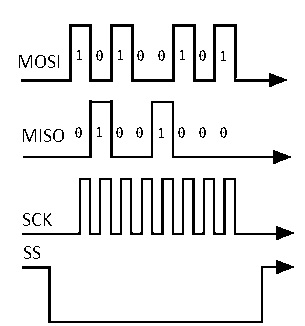

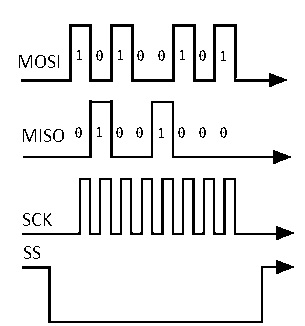

SPI – , .

SPI «-». MOSI SCLK, . MISO, . SS.

SPI

UART – – , .

RxD ( ) TxD ( ).

UART TxD . . UART , , UART , . , . 8 ( ), , .

UART «-». , UART . « » «».

UART

, .

, (, .) . , .

, . , , , .. , . . – , . , . , .

, .

( ), :

- «-»;

- «»;

- «» («»).

«-» — , . , — .

«» (, « » «») , . . , , , . .

( «») . , , , - . .

:

- ;

- ;

- -.

, . . . , .

, . , , .

(-/)

:

- ();

- ();

- ().

. .

, .

: , «» .

. .

:

- ;

- .

. . . ( – , – , , ). « » ( ). .

, , .

?

() SPI I2C UART.

I2C

I2C – . I2C . I2C «-», .

, , . , . 7- 16 . , 112 . I2C (SDA) (SCL).

I2C

SPI

SPI – , .

SPI «-». MOSI SCLK, . MISO, . SS.

SPI

UART

UART – – , .

RxD ( ) TxD ( ).

UART TxD . . UART , , UART , . , . 8 ( ), , .

UART «-». , UART . « » «».

UART

ما هو هذا DAC؟

لا يبدو هذا واحدًا

أولاً ، دعنا نحدد DAC / ADC المستخدم:

لوحة تصحيح الأجهزة التناظرية AD9993-EBZ عبارة عن جهاز يجمع أربعة ADCs 14 بت واثنين من DACs 14 بت.

يتم التحكم في أوضاع تشغيل IC عن طريق تغيير حالة سجلاتها الداخلية. يستخدم AD9993 66 تسجيلًا بحجم كلمات مخزن (معالج) يبلغ 8 بتات ، ويتم وصف عناوينها بقيم سداسية عشرية من ثلاثة أرقام (12 بت بيانات). يتم دعم نوعين من الأوامر - قراءة الأمر وكتابة الأمر. بمعنى آخر ، من أجل تصحيح تشغيل IC ، من الضروري إرسال أمر لكتابة بعض القيمة الصالحة ذات 8 بت إلى عنوان تسجيل محدد. يتم الوصول إلى سجلات IC من خلال الواجهة الطرفية التسلسلية (SPI) ، والتي يتم تحقيق الاتصال بها على لوحة التطوير من خلال موصل FIFO_0 ذي 40 سنًا أو من خلال مجموعة جهات اتصال مثبتة بشكل إضافي.

مثل هذا (FIFO_0 - أعلى موصل رمادي)

المتطلبات الأساسية لمعلمات حد SPI:

- الحد الأقصى لتردد نقل البيانات - 25 ميجا هرتز ؛

- مدة المستويين العلوي والسفلي على خط توليد إشارة المزامنة هي 10 نانوثانية ؛

- وقت ضبط المستوى على خطوط نقل البيانات وعلى خطوط الدقة - 2 نانوثانية ؛

- وقت تثبيت المستوى على خطوط نقل البيانات وعلى خط الاستبانة - 2 نانوثانية ؛

- الوقت المضمون لصلاحية بتة بيانات واحدة على خط نقل التابع هو 2 نانوثانية.

يمكن العثور على وصف كامل لميزات الجهاز في وثائقه .

ماذا تقول الشركة المصنعة؟

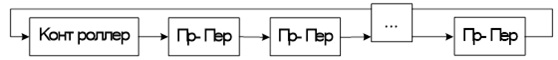

مخطط التحكم الموصى به

استنادًا إلى وثائق AD9993-EBZ ، فإن الطريقة الموصى بها للتحكم في IC هي استخدام لوحة تصحيح أخطاء الأجهزة التناظرية HSC-ADC-EVALC المتصلة بـ IC عبر منفذ 40 سنًا وجهاز كمبيوتر عبر واجهة USB.

يستخدم SPIController كبرنامج تحكم. الأجهزة التناظرية

الموصى بها

دارة HSC-ADC-EVALC (بناءً على Xilinx Virtex-4 FPGA)

سلبيات:

- غالي السعر. يتم تقديم لوحة التصحيح HSC-ADC-EVALC على الموقع الرسمي للأجهزة التناظرية مقابل 698.28 دولارًا.

- واجهة مستخدم غير ملائمة. لا يوفر برنامج SPIController ، بالإضافة إلى الوظيفة الرئيسية لسجلات الكتابة والقراءة ، القدرة على حفظ الأوامر أو البدء المجدول لها.

- . SPI SPIController, . Analog Devices, SPI.

SPIController

:

- .

HSC-ADC-EVALC

وتجدر الإشارة إلى أن استخدام لوحة HSC-ADC-EVALC للأجهزة التناظرية كجهاز تحكم DAC / ADC ليس الغرض الرئيسي منها.

يتم استخدام HSC-ADC-EVALC بشكل أساسي كبطاقة ذاكرة مؤقتة لـ ADC ، ومع ذلك فهي تتمتع أيضًا بوظيفة تكوين بطاقات التصحيح عبر SPI إذا كانت البطاقات المتصلة تدعمها.

نموذج التفاعل الخاص

سبب استخدام جهاز وسيط

من الواضح أن التفاعل بين DAC / ADC والكمبيوتر الشخصي لا يمكن تنظيمه بشكل مباشر ، لأن SPI ، الذي تمت برمجة AD9993-EBZ به ، ليس واجهة نموذجية لجهاز كمبيوتر حديث.

لحل هذه المشكلة ، كان من الضروري استخدام جهاز وسيط يقوم بتحويل البيانات من واجهة USB المرسلة من الكمبيوتر إلى تنسيق واجهة SPI المدعوم من IC.

أثناء العمل على الخيارات ، وقع الاختيار على استخدام لوحة تصحيح أخطاء Terasic DE10-Nano ، استنادًا إلى Cyclone V FPGA.

نموذج التفاعل الخاص

لماذا FPGA رائع جدًا؟

المزايا الرئيسية لاستخدام FPGAs:

- . DE10-Nano , , , . IDE, Verilog.

- . DE10-Nano HSC-ADC-EVALC ($110 $698.28). DE10-Nano , .

- . , .

- . FPGA- (FPGA – field-programmable gate array – , ), ( ). rocketboards c .

...

أثناء تصميم نموذج التفاعل ، تقرر تنفيذ واجهة SPI بناءً على GPIO (دبابيس للأغراض العامة) ، والتي تتوفر قاعدة الاتصال الخاصة بها على DE10-Nano. لا ينبغي أن يتسبب تطبيق وحدة التحكم SPI المستندة إلى FPGA في حدوث أي مشاكل خاصة بسبب الكمية الكبيرة من المواد حول موضوع مشابه.

ومع ذلك ، فإن تنفيذ توصيل FPGA بالكمبيوتر عبر واجهة USB تسبب في صعوبات.

يحتوي DE10-Nano على منافذ USB التالية:

- USB mini-B مدعوم بشريحة FT232R ، مما يحقق اتصال UART بـ USB.

- يتم التحكم في USB mini-B بواسطة شريحة SMSC USB3300 ، والتي تنفذ الطبقة المادية لواجهة USB ، وتستخدم أيضًا لبرمجة FPGAs.

استخدام هذه المنافذ معقد بسبب حقيقة أن DE10-Nano يتواصل مع هذه المنافذ من خلال ما يسمى HPS ( نظام المعالج الصلب ) - وهو جزء من شريحة Cylone V ، والذي يحتوي على وحدة معالج دقيق ، ومعالج ARM Cortex ، ووحدات تحكم ذاكرة فلاش وغير ذلك الكثير. يتمثل الاختلاف الرئيسي بين HPS و FPGAs في أن HPS عبارة عن كتل ذات بنية ثابتة ، ومُحسَّنة لوظيفة معينة وليس لديها أدوات البرمجة الخاصة بها (وبالتالي فهي صلبة).

أجزاء HPS و FPGA من شريحة Cyclone V لها دبابيس خاصة بها. لا يتم مشاركة هذه المسامير بحرية بين HPS و FPGA. يتم تكوين جهات اتصال HPS بواسطة برنامج يعمل في HPS. تتم برمجة دبابيس FPGA باستخدام صورة تكوين FPGA عبر HPS أو أي مصدر خارجي آخر مدعوم.

من أجل تنظيم تفاعل المنطق القابل للبرمجة لشريحة Cyclone V مع هذه المنافذ ، من الضروري إنشاء محمل إقلاع Linux خاص يعمل على HPS ، وأيضًا من الضروري تطوير برنامج قادر على نقل الإشارات من وحدات التحكم في منافذ USB المتاحة إلى جهات الاتصال المجانية لـ FPGA.

في المرحلة الحالية من المعرفة ، تبين أن هذا السؤال ساحق ، لذلك تقرر إيجاد طريقة أخرى. ومع ذلك ، بالنسبة للأشخاص الذين يواجهون مشكلة مماثلة وقرروا اكتشافها ، قد يكون من المفيد قراءة مقال حول حل ممكن.

هناك مخرج!

بعد البحث عن الإنترنت بدقة ، تقرر استخدام وحدة تحكم UART خارجية.

وحدة التحكم الخارجية UART عبارة عن لوحة صغيرة تعتمد على شريحة FT232RL. تحتوي اللوحة على موصلات miniUSB-B للاتصال بجهاز كمبيوتر وموصل ذي 6 سنون للتواصل مع وحدات التحكم الدقيقة والأجهزة.

يتم توصيل وحدة التحكم عبر واجهة USB بجهاز الكمبيوتر ، وعبر قاعدة اتصال GPIO بـ DE10-Nano.

وحدة التحكم نفسها من Waveshare (المستخدمة في المشروع)

إن استخدام واجهة UART عبر USB لنقل البيانات من جهاز كمبيوتر يلغي فعليًا الحاجة إلى التعامل مع جهاز بروتوكول USB المعقد ومتعدد الطبقات. من الآن فصاعدًا ، لم يعد التفاعل عبر واجهة USB مصدر قلق لنا ، حيث تم تعيين هذه المهمة إلى برامج التشغيل المثبتة مسبقًا في النظام أو التي تم تثبيتها بشكل مستقل بواسطة المستخدم.

بالإضافة إلى خطوط الطاقة والأرض ، بالإضافة إلى خطوط نقل واستقبال البيانات ، توجد دبابيس على اللوحة تحمل علامة RTS و CTS. تُستخدم جهات الاتصال هذه لما يسمى بالتحكم في التدفق - وهي آلية مصممة للإشارة إلى الاستعداد لاستقبال البيانات من الجهاز الرئيسي أو الجهاز التابع ، اعتمادًا على حالة الخطوط. لا يعد استخدام هذه الخطوط ضروريًا ، لذلك ، لتعطيل الآلية ، من الضروري الإشارة في إعدادات برنامج تشغيل الكمبيوتر إلى عدم استخدام التحكم في التدفق (عادةً ما يكون هذا هو التكوين الافتراضي).

عند الاتصال بجهاز كمبيوتر يعمل بنظام Windows ، يتم اكتشاف وحدة التحكم UART كمنفذ تسلسلي افتراضي. لذلك ، فإن تطوير مخطط للتفاعل مع جهاز كمبيوتر يأتي إلى إنشاء برنامج بوظيفة التفاعل مع منفذ افتراضي تسلسلي ، بالإضافة إلى تطوير مشروع لـ FPGA يقوم بتنفيذ استقبال / إرسال البيانات عبر واجهة UART.

تعتبر وحدة التحكم الخارجية UART ، في الواقع ، نظيرًا مطلقًا لوحدة التحكم الموجودة بالفعل على DE10-Nano ، ولكن ميزتها الوحيدة هي القدرة على الاتصال مباشرة بدبابيس FPGA المجانية. تتراوح تكلفة هذا الجهاز من 5 دولارات إلى 10 دولارات.

تطوير البرمجيات

معلومات عامة

كما ذكرنا سابقًا ، يتم تقليل تطوير البرامج للكمبيوتر الشخصي إلى إنشاء برنامج يدعم تبادل المعلومات باستخدام منفذ تسلسلي افتراضي. أثناء تحليل أدوات البرمجيات المتاحة لتطوير البرمجيات ، وقع الاختيار على لغة برمجة الإصدار الثامن من Java باستخدام مكتبة RTXT.

Java هي لغة برمجة موجهة للكائنات مكتوبة بقوة مع عدد من الميزات الرئيسية. على وجه الخصوص ، يتم ترجمة البرامج المكتوبة بلغة برمجة Java إلى رمز ثانوي خاص ، مما يسمح لها بالعمل على أي بنية كمبيوتر يتم تنفيذ جهاز Java الظاهري لها.

لا تمتلك مكتبات Java القياسية القدرة على التفاعل مع المنفذ التسلسلي الظاهري. هذا ما تم استخدام مكتبة RTXT من أجله. يتم توزيع RTXT بموجب ترخيص برنامج مجاني. تستخدم المكتبة نظام تنفيذ التفاعل مع الواجهات وتوفر فئات لعمليات التحليل والتوصيل والقراءة والكتابة باستخدام المنفذ التسلسلي. يمكن العثور على المزيد حول هذه المكتبة هنا .

تُستخدم مكتبة Swing المدمجة القديمة والموثوقة كأداة لتطوير واجهة المستخدم. نظرًا للقدرة على تغيير السمات ، قد لا تبدو واجهة المستخدم البسيطة في Swing

البرنامج نفسه بسيط للغاية ويستخدم بشكل أساسي الإمكانات الموثقة لمكتبة RTXT.

الوظيفة الرئيسية للبرنامج

هذه هي الطريقة التي يتم بها تحديد المنافذ المتاحة:

public String[] getPorts() {

ports = CommPortIdentifier.getPortIdentifiers();

while (ports.hasMoreElements()) {

CommPortIdentifier curPort = (CommPortIdentifier) ports.nextElement();

if (curPort.getPortType() == CommPortIdentifier.PORT_SERIAL) {

portMap.put(curPort.getName(), curPort);

}

}

return portMap.keySet().toArray(new String[0]);

}

الاتصال بالمنفذ المحدد:

public void connect() {

String selectedPort = (String)gui.ports.getSelectedItem();

selectedPortIdentifier = portMap.get(selectedPort);

CommPort commPort;

try{

commPort = selectedPortIdentifier.open("UART controller", TIMEOUT);

serialPort = (SerialPort)commPort;

serialPort.setSerialPortParams(BAUD_RATE, SerialPort.DATABITS_8, SerialPort.STOPBITS_1, SerialPort.PARITY_NONE);

gui.writeLog(selectedPort + " opened successfully.");

}catch (PortInUseException e){

gui.writeLogWithWarning(selectedPort + " is in use. (" + e.toString() + ")");

}catch (Exception e){

gui.writeLogWithWarning("Failed to open " + selectedPort + " (" + e.toString() + ")");

}

}

عملية نقل البيانات:

public boolean writeData(byte[] bytes){

boolean successfull = false;

try {

gui.writeLog("WRITING: " + HexBinUtil.stringFromByteArray(bytes));

output.write(bytes);

output.flush();

successfull = true;

}

catch (Exception e) {

gui.writeLogWithWarning("Failed to write data. (" + e.toString() + ")");

}

return successfull;

}

جار استقبال البيانات:

public void serialEvent(SerialPortEvent serialPortEvent) {

if (serialPortEvent.getEventType() == SerialPortEvent.DATA_AVAILABLE) {

try {

byte singleData = (byte)input.read();

gui.writeLog("READING: " + HexBinUtil.stringFromByteArray(singleData));

}

catch (Exception e) {

gui.writeLogWithWarning("Failed to read data. (" + e.toString() + ")");

}

}

}

كما ذكرنا سابقًا ، يتم التحكم في DAC / ADC عن طريق إرسال أمر لكتابة بعض القيمة الصالحة ذات 8 بت إلى عنوان تسجيل محدد موصوف في الوثائق. لتحديد الحالة الحالية للسجل ، يجب عليك إرسال أمر read وتحديد عنوان السجل المطلوب. الوصف الكامل كما هو الحال دائمًا في الوثائق .

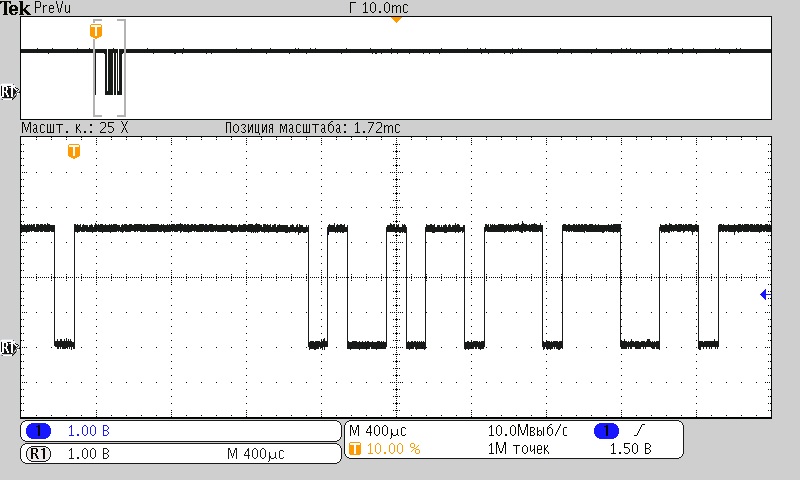

نقل البيانات UART

أثناء دراسة AD9993-EBZ ، وجد أنه يتم استخدام 8 بتات بيانات فقط في مساحة عنوان السجل المتوفرة ذات 12 بت. أيضًا ، يتم وصف القيمة المرسلة لحالة التسجيل بـ 8 بتات. لتحديد نوع نقل البيانات (كتابة / قراءة) ، يلزم نقل 1 بت بيانات.

نظرًا لأن القيد الحالي على الحد الأقصى لحجم الرسالة عبر واجهة UART هو 8 بتات بيانات ، فقد تقرر إرسال 3 رسائل متتالية 8 بت أثناء عملية الكتابة ورسالتين أثناء عملية القراءة.

سيحتوي الطرد الأول على نوع نقل البيانات ، المكرر لحجم الطرد بالكامل. لذلك ، يمكن أن يكون هناك قيمتان محتملتان فقط: 00000000 للقراءة و 11111111 للكتابة ، على التوالي. تم استخدام رشقة عدد صحيح لإرسال بتة بيانات واحدة لتبسيط المعالجة الإضافية للإشارات المستقبلة.

بعد ذلك ، يتم إرسال عنوان السجل المطلوب والقيمة المرسلة لحالة التسجيل أثناء عملية التسجيل.

مخطط الذبذبات لحزمة UART المطورة

واجهة المستخدم

العناصر الرئيسية لواجهة مستخدم البرنامج هي أزرار للاتصال / الفصل من المنافذ التسلسلية المتاحة (العناصر 3،4) ، وحقول إدخال العنوان وقيم التسجيل (العناصر 7،8) ، ونافذة السجل (العنصر 6). تم تصميم البرنامج للتفاعل معه في حالتين: "متصل بالمنفذ" و "غير متصل بالمنفذ". تحدد الدول نشاط بعض العناصر على واجهة البرنامج ، كما تقيد تنفيذ طرق معينة لتقليل احتمالية الأخطاء والاستخدام غير الصحيح للبرامج. عند التمكين ، يكون البرنامج في حالة "مفصول من المنفذ". أيضًا ، لتسهيل العمل مع البرنامج (والذي كنت أحد الأهداف الرئيسية للمشروع) ، تمت إضافة وظيفة توصيل الملفات بالأوامر المحفوظة بالفعل بتنسيق JSON (العنصر 10).

عملية تحميل الأوامر: واجهة أوامر

تحديد الملف تتيح لك الوظيفة فرز الأوامر المحملة إلى أقسام (العنصر 12) ، وتخصيص عملية العمل مع الأوامر المتصلة (سواء لإرسال أمر إلى المنفذ التسلسلي فور الضغط عليه ، أو ملء حقول وقيم العنوان وفقًا للأمر المحدد) ...

تطوير مشروع FPGA

معلومات عامة

قبل أن تبدأ في تطوير مشروع لـ FPGA ، عليك أن تقرر المهمة التي يجب أن يحلها.

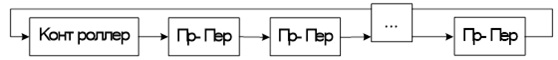

يبدو الأمر كالتالي: يجب أن يدعم مشروع FPGA تحويل البيانات التالي:

مخطط تحويل البيانات

يستقبل DE10-Nano إشارات من خط Tx لواجهة UART (الإشارة العلوية). بعد ذلك ، يحتاج FPGA إلى تحديد البيانات المستلمة بشكل صحيح من ثلاث رسائل كل منها 8 بتات وتحويلها إلى تنسيق رسالة SPI المطابق للوثائق (مقدمة في 4 أسطر).

الوحدات الرئيسية المطلوبة لتنفيذ هذا التحويل هي وحدة تحكم UART ووحدة تحكم SPI. بالنسبة لهم يتم تعيين باقي الفصل.

عند تطوير مشاريع FPGAs ، تم استخدام الإصدار 17 من IDE Qartus Prime Lite Edition.

إذا لم تكن لديك خبرة في استخدام Quartus أو لم تقم ببرمجة FPGA على الإطلاق ، فمن المستحسن أن تبدأ بمثال مفهوم (في رأيي) عن المشروع الأول في Quartus.

أود أن أشير إلى أن جميع المقتطفات من كود Verilog الموضحة أدناه عبارة عن مجموعة من الحلول الموجودة على الإنترنت ، والتي لا تدعي أنها أي أصالة. مرة أخرى ، الهدف الرئيسي لهذا المشروع هو حل مشكلة معينة.

تحكم UART

وصف

تتكون وحدة التحكم UART من ثلاث وحدات:

- مولد النبض

- وحدة التسجيل

- وحدة القراءة.

يوصى بإلقاء نظرة على هذه المقالة ، التي تم أخذ معظم المعلومات منها. علاوة على ذلك ، سأركز فقط على أهم تفاصيل التنفيذ (في رأيي).

مولد النبض

نظرًا لأن واجهة UART غير متزامنة ، يحتاج جهاز الاستقبال إلى إنشاء إشارة مرجعية خاصة به لاستقبال الإشارة المرسلة بشكل صحيح ، مما يسمح له بتحديد بداية جزء جديد من المعلومات بشكل صحيح.

هناك مجموعة مقبولة بشكل عام من معدلات البث بالباود UART القياسية: 300؛ 600 ؛ 1200 ؛ 2400 ؛ 4800 ؛ 9600 ؛ 19200 ؛ 38400 ؛ 57600 ؛ 115200 ؛ 230400 ؛ 460800 ؛ 921600 باود في حالتنا ، يحدث نقل البيانات عند 9600 باود. بعد ذلك ، نحتاج إلى الحصول على مولد بتردد 16 ضعف معدل الرمز. يعد ذلك ضروريًا للكشف عن مستوى الإشارة المرسلة بشكل صحيح.

لتوليد نبضات ، يتم استخدام مولد 50 ميغا هرتز على الشريحة. للحصول على التردد المطلوب ، يجب مراعاة كل 325 نبضة للمولد.

هكذا ستبدو في Verilog:

input Clk; // 50

input Rst_n; //

input [15:0] BaudRate; // , 325

output Tick; //

reg [15:0] baudRateReg; //

always @(posedge Clk or negedge Rst_n)

if (!Rst_n) baudRateReg <= 16'b1;

else if (Tick) baudRateReg <= 16'b1;

else baudRateReg <= baudRateReg + 1'b1;

assign Tick = (baudRateReg == BaudRate);

endmodule

وحدة القارئ

يقوم القارئ بتحويل إشارة الإدخال من خط RX إلى مصفوفة بيانات إخراج 8 بت.

القراءة المباشرة لبيانات القراءة ونقلها إلى المخرجات:

input Clk, Rx,Tick; // 50, Rx,

input [3:0]NBits; // , 8

output RxDone; //

output [7:0]RxData; //

reg read_enable = 1'b0; //

reg RxDone = 1'b0; //

reg [3:0] counter = 4'b0000; //

reg start_bit = 1'b1; //

reg [4:0]Bit = 5'b00000; //

reg [7:0] RxData; //

reg [7:0] Read_data= 8'b00000000; //

always @ (posedge Tick) //

begin

if (read_enable)

begin

RxDone <= 1'b0; //

counter <= counter+1'b1; //

if ((counter == 4'b1000) & (start_bit)) //

begin

start_bit <= 1'b0;

counter <= 4'b0000;

end

if ((counter == 4'b1111) & (!start_bit) & (Bit < NBits)) //

begin

Bit <= Bit+1'b1;

Read_data <= {Rx,Read_data[7:1]};

counter <= 4'b0000;

end

if ((counter == 4'b1111) & (Bit == NBits) & (Rx)) //

begin

Bit <= 4'b0000;

RxDone <= 1'b1; //

counter <= 4'b0000; //

start_bit <= 1'b1; //

end

end

end

always @ (posedge Clk)

begin

if (NBits == 4'b1000) // 8 ,

begin

RxData[7:0] <= Read_data[7:0];

end

end

وحدة الإرسال

تقوم وحدة الإرسال بتحويل إشارة الإدخال 8 بت إلى حزمة بيانات تسلسلية UART.

نقل البيانات المباشر:

input Clk, Rst_n, TxEn; // 50, ,

input Tick; //

input [3:0]NBits; //

input [7:0]TxData;

output Tx;

output TxDone;

reg Tx;

reg TxDone = 1'b0;

reg write_enable = 1'b0;

reg start_bit = 1'b1;

reg stop_bit = 1'b0;

reg [4:0] Bit = 5'b00000;

reg [3:0] counter = 4'b0000;

reg [7:0] in_data=8'b00000000;

always @ (posedge Tick) //

begin

if (!write_enable)

begin

TxDone = 1'b0;

start_bit <=1'b1;

stop_bit <= 1'b0;

end

if (write_enable)

begin

counter <= counter+1'b1; //

if(start_bit & !stop_bit)//

begin

Tx <=1'b0;

in_data <= TxData;

if ((counter == 4'b1111) & (start_bit) ) //

begin

start_bit <= 1'b0;

in_data <= {1'b0,in_data[7:1]};

Tx <= in_data[0];

end

if ((counter == 4'b1111) & (!start_bit) & (Bit < NBits-1)) //

begin

in_data <= {1'b0,in_data[7:1]};

Bit<=Bit+1'b1;

Tx <= in_data[0];

start_bit <= 1'b0;

counter <= 4'b0000;

end

if ((counter == 4'b1111) & (Bit == NBits-1) & (!stop_bit)) //

begin

Tx <= 1'b1;

counter <= 4'b0000;

stop_bit<=1'b1;

end

if ((counter == 4'b1111) & (Bit == NBits-1) & (stop_bit) ) //

begin

Bit <= 4'b0000;

TxDone <= 1'b1;

counter <= 4'b0000;

//start_bit <=1'b1;

end

end

end

تحكم SPI

استطراد مهم

نظرًا لأن وحدة التحكم SPI ، التي يتم تنفيذها على أساس FPGA ، هي بنية منطقية أكثر تعقيدًا من وحدة التحكم UART ، فإن التفسير الإضافي لمنطق التشغيل يكون أسهل في التنفيذ على نموذج الدائرة لوحدة التحكم.

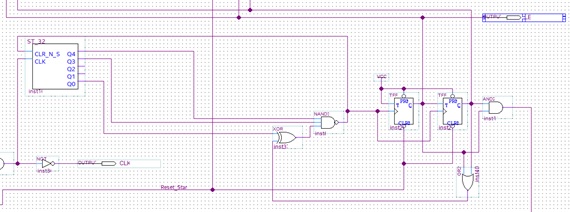

المخطط العام لوحدة التحكم

يمكن تقسيم النموذج المطور إلى 3 وحدات رئيسية:

- وحدة الكتابة المتسلسلة

- وحدة عداد بت

- وحدة محلل الأخطاء.

يعتبر التقسيم إلى وحدات تعسفية إلى حد ما ، لأن الدائرة لديها اتصال عالي بين العناصر المستخدمة. يعتمد التقسيم على المهام التي تؤديها المجموعات الفردية للعناصر المعروضة في الرسم البياني العام.

يتم توفير توقيت الدائرة بواسطة إشارة 12.5 ميجا هرتز يتم توفيرها عبر خط CLK_125.

يتم تنفيذ بدء عمل وحدة التحكم على تكوين رسالة تحكم بواسطة إشارة "START". من خلال هذه الإشارة ، يتم ضبط جميع وحدات الدائرة على حالتها الأولية ويتم تهيئة بداية دورة توليد الإشارات المطلوبة على خطوط الإخراج CLK و SS و MOSI لواجهة SPI

وحدة الكتابة المتسلسلة

ستؤدي وحدة الكتابة التسلسلية المهمة الرئيسية لوحدة التحكم SPI ، وهي إخراج بيانات البت المتوازي إلى خط MOSI التسلسلي. ويرجع ذلك إلى عنصر RG_24_PI_SO ، الذي يعمل على مبدأ سجل التحول القائم على D-flip-flops.

يحتوي عنصر RG_24_PI_SO على 24 إدخال بيانات يتوافق مع وثائق AD9993-EBZ في تنسيق إرسال SPI. يشملوا:

- بيانات الأمر (DATA_0 - DATA_7) ؛

- تسجيل بيانات العنوان (ADR_0 - ADR_12) ؛

- W / R الكتابة / وضع القراءة بت.

تتم كتابة الإشارات المقدمة بالتوازي على مستوى منطقي "1" عند إدخال LoadP_ShiftN. علاوة على ذلك ، عند المستوى المنطقي "0" عند إدخال LoadP_ShiftN ، في كل دورة ساعة عند إدخال CLK ، يقوم العنصر بإعادة إنتاج البيانات المسجلة بالتناوب إلى السطر التسلسلي لإخراج MOSI.

وحدة عداد بت

وحدة عداد البت مطلوبة لتحديد مدة إشارة تمكين كتابة البيانات على خط SS لواجهة SPI. نظرًا لأنه وفقًا لوثائق AD9993-EBZ ، يجب أن تكون مدة إشارة التمكين مساوية للمدة الإجمالية للبيانات المرسلة ، يصبح من الضروري حساب 24 نبضة متزامنة من بداية إرسال البيانات لتحديد المدة المطلوبة لإشارة التمكين. يتم تنفيذ وظيفة العد بواسطة عنصر ST_32 ، والذي عند اكتشاف إشارة الساعة 24 ، يقوم بإعادة إنتاج إشارة تُستخدم لإعادة ضبط العداد ، وكذلك لإنهاء إشارة التمكين المرسلة.

بالإضافة إلى الوظيفة الرئيسية ، فإن وحدة عداد البت مسؤولة أيضًا عن تهيئة عملية تحليل الخطأ ، حيث يتمثل الإجراء الأولي في إرسال أمر قراءة القيمة إلى عنوان آخر سجل مسجل. نظرًا لأنه يجب بدء عملية تحليل الخطأ بعد فاصل زمني مكافئ لمدة 23 نبضة متزامنة من لحظة إرسال آخر بتة بيانات مرسلة (تم إنشاؤها تجريبيًا) ، يتحول عداد البت بعد إعادة تعيين الإشارة إلى وضع عد نبض المزامنة 23 ، مما يضمن تشغيل عملية تحليل الخطأ.

وحدة تحليل الأخطاء

كما هو مذكور في شرح الوحدة السابقة ، لتوفير وظيفة تحليل الأخطاء ، تم تطوير طريقة بناءً على قراءة قيمة الأمر المخزن على IC في عنوان التسجيل المستخدم في عملية تسجيل البيانات. عملية القراءة ضرورية لمقارنة القيمة المكتوبة ببيانات القراءة لتحديد التناقضات ، وبالتالي لتحديد الخطأ الذي حدث. تعتمد وحدة تحليل الأخطاء على عنصر RG_8_SI_PO ، الذي يعمل على مبدأ سجل التحول. يقوم العنصر بتحويل الإشارات المستلمة عبر منفذ MISO التسلسلي إلى خرج 8 بت متوازي. ثم تتم مقارنة البيانات مع قيمة الأمر المستخدم أثناء عملية تسجيل البيانات. يتم تنفيذ وظيفة المقارنة بواسطة عنصر CMP_8 بناءً على المنطق الحصري. إذا تم العثور على تناقض ،تنقل الوحدة إشارة إلى خرج LED ، والتي ستكون في حالة الوحدة المنطقية حتى عملية تسجيل البيانات التالية من المفترض أن خرج LED سيتم توصيله بأحد مصابيح LED ، والتي توجد مجموعة منها على لوحة تطوير DE10 Nano ، والتي ستشير بصريًا إلى حدوث خطأ.

خاتمة

نتيجة لحل هذه المشكلة ، تم تصميم مخطط التفاعل بين الكمبيوتر وجهاز DAC / ADC وتنفيذه فعليًا مع عدد من المزايا الرئيسية. في عملية التنفيذ ، تم حل مشكلة اتصال FPGA والكمبيوتر الشخصي. كان الحل لهذا هو استخدام وحدة UART خارجية. تمت كتابة برنامج الكمبيوتر الشخصي بلغة Java. يحتوي البرنامج على واجهة ذات إمكانيات أساسية لإرسال واستقبال البيانات بتنسيق إرسال UART المطور ، بالإضافة إلى أنه يحتوي على وظيفة تحميل الأوامر المحفوظة. تم تطوير وحدات التحكم UART و SPI المستندة إلى FPGA.

تسمح القضايا التي تم بحثها في إطار هذا المشروع بما يلي:

- تقييم طرق تفاعل الدوائر المتكاملة مع الأجهزة الخارجية ؛

- تقييم طرق استخدام FPGA كجهاز مطابق ، ومخزن مؤقت لتبادل البيانات ؛

- استكشاف واحدة من أكثر الأساليب فعالية لتطوير البرمجيات للاستخدام العملي.

ملاحظة: سأكون سعيدًا بأي إضافات أو ملاحظات أو دلائل على وجود أخطاء.