هل تريد أن تعرف كيف تحصل على وظيفة في تصميم إلكترونيات سفينة الفضاء؟ تلقيت مؤخرًا عرضًا لإجراء مقابلة لمنصب مصمم FPGA لشركة Blue Origin (انظر أعلاه). أنا شخصياً لست بحاجة إلى مثل هذا المنصب (لدي بالفعل منصب مصمم ASIC في شركة أخرى) ، لكنني لاحظت أن المتطلبات الفنية للمتقدمين في Blue Origin تتطابق تمامًا مع محتوى الندوة لأطفال المدارس والطلاب الصغار ، والتي ستعقد في 15-17 سبتمبر في معرض ChipEXPO في سكولكوفو ، بدعم من RUSNANO. على الرغم من أننا بالطبع سنتطرق في الندوة إلى تقنيات Verilog و FPGA في المستوى الأولي للغاية: مفاهيم أساسية وأمثلة بسيطة ولكنها مثيرة للاهتمام بالفعل. للحصول على وظيفة بعد ذلك في Blue Origin ، ما زلت بحاجة إلى بضع سنوات من الدراسة والعمل.

بسبب فيروس كورونا ، ستكون الندوة بعيدة ، لذلك لن يشارك فقط تلاميذ المدارس وطلاب موسكو ، ولكن أيضًا كل من روسيا وأوكرانيا وكازاخستان وكاليفورنيا ودول ومناطق أخرى. سيقوم المحاضرون والمهندسون من MIET و HSE MIEM و MIPT وجامعة Chernihiv Polytechnic وجامعة Samara و IVA Technologies و fpga-systems.ru بإجراء محاضرات جسدية ومساعدة المشاركين عن بُعد .

للمشاركة أولاً ، حتى قبل الندوة ، تحتاج إلى إكمال ثلاثة أجزاء من الدورة النظرية من RUSNANO ، تحت العنوان العام "كيف يعمل مبتكرو الرقائق النانوية الذكية": "من الترانزستور إلى الدوائر الدقيقة" ، "الجانب المنطقي للدوائر الرقمية" ، "الجانب المادي للدوائر الرقمية". هذه الدورة ضرورية حتى تفهم ما تفعله خلال ورشة العمل. عند الحصول على شهادة إتمام الدورة النظرية عبر الإنترنت ، يمكنك الذهاب إلى مكتب RUSNANO في موسكو والحصول على رسوم مجانية لحضور ندوة عملية (إذا بقوا ، يكون لأطفال المدارس الأولوية). مع هذا المنتدى يمكنك العمل في المنزل ، قبل وأثناء وبعد ندوة سكولكوفو.

كيفية جني الأموال والاستعداد للندوة وماذا سيكون عليها:

يمكنك العثور على إرشادات حول كيفية الحصول على رسوم على موقع STEMford الإلكتروني . STEMford هي برامج تعليمية لأطفال المدارس من eNano ، وهي شركة تابعة لمؤسسة RUSNANO للبرامج التعليمية للبنية التحتية. هنا مكتبهم للزيارة:

قبل المعمل ، ستحتاج إلى تثبيت Intel Quartus Prime Lite Edition على جهاز الكمبيوتر الخاص بك. تعليمات حول كيفية القيام بذلك موجودة في الجزء المجاني من كتاب "التركيب الرقمي: دورة عملية" الذي حرره أ. يو رومانوف ، يو في بانشول. DMK Press ، 2020.

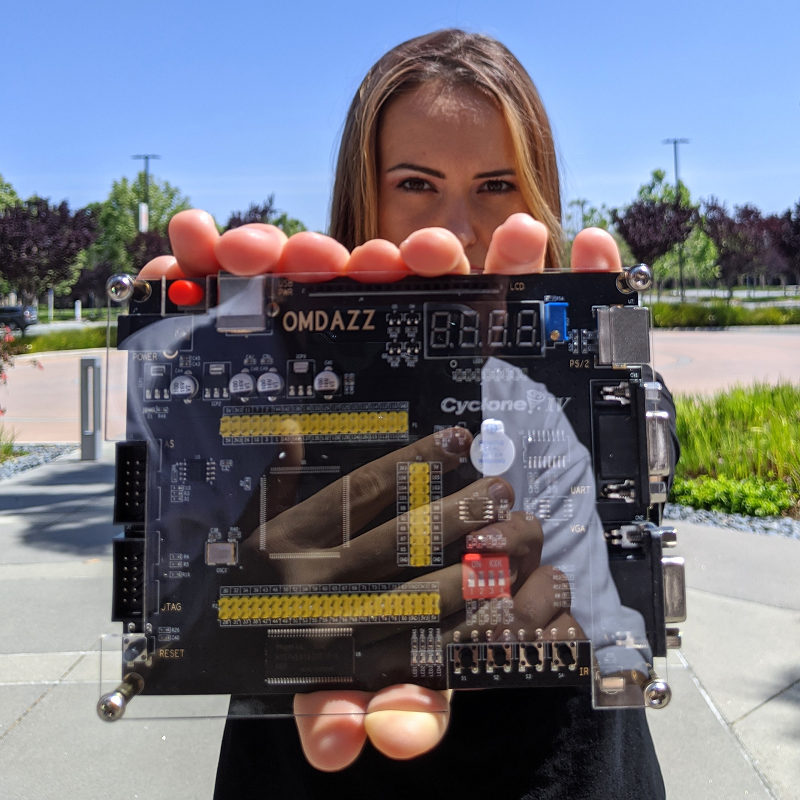

بشكل عام ، يعتبر "Digital Synthesis" كتابًا مفيدًا لندوة ، فهو يصف التمارين التي سيتم تقديمها مع بعض الاختلافات في الندوة ، على الرغم من أنه على سبيل المثال ، بدلاً من المعالج التعليمي schoolMIPS ، أكثر حداثةschoolRISCV : في نهاية كتاب التوليف الرقمي ، هناك مقابلة مسلية إلى حد ما مع زوجين من المتزوجين حديثًا فلاديسلاف وإيلينا شارشين ، والتي جلبت مع زميلهما أندري بابوشين إنتل إلى كاليفورنيا للفوز الفضي في مسابقة InnovateFPGA: إليك إحدى اللوحات التي سيتم استخدامها في الندوة. إذا لم تكن هناك لوحات كافية لك ، أو إذا لم تكن طالبًا ، يمكنك طلب لوحة على AliExpress وفي أماكن أخرى: 1 ، 2 ، 3 ، 4 : ماذا سيحدث في الندوة؟ فيما يلي أجزاء البرنامج :

15 . .

: , « » ().

15.00. , .

15.15-15.30. -: Apple iPhone: .

, . , .

15.30-16.00. : Verilog. /FPGA Intel Quartus Prime Lite Edition. .

16.00-16.30.

///-, , c .

16.30-17.00. .

17.00-17.30. : , .

17.30-18.00. .

18.00-19.00. ZEOWAA OMDAZZ Intel FPGA Cyclone IV: : ( ). Terasic DE10-Lite Intel FPGA MAX10: : ( ).

19.00-21.00. , : , , ,

.

يعتمد اليوم الأول على تجربة عقد ندوة العام الماضي في موسكو ، والتي تم وصفها في مقال على موقع حبري :

اليوم الثاني يعتمد على تجربة إقامة مدرسة صيفية في زيلينوغراد العام الماضي وندوات في سامارا:

16 . .

: , , , .

15.00-15.15. -: : , .

.

15.15-15.30. : VGA.

.

15.30-16.00. .

16.00-16.30. . Digilent Basys3 Xilinx FPGA Artix-7. .

, fpga-systems.ru.

16.30-17.00. ZEOWAA, OMDAZZ Terasic DE10-Lite.

.

17.00-17.30. : Linear Feedback Shift Registers (LFSR) . Verilog VHDL LFSR . LFSR VGA .

, .

17.30-18.00. ZEOWAA, OMDAZZ Terasic DE10-Lite.

.

18.00-19.00. .

.

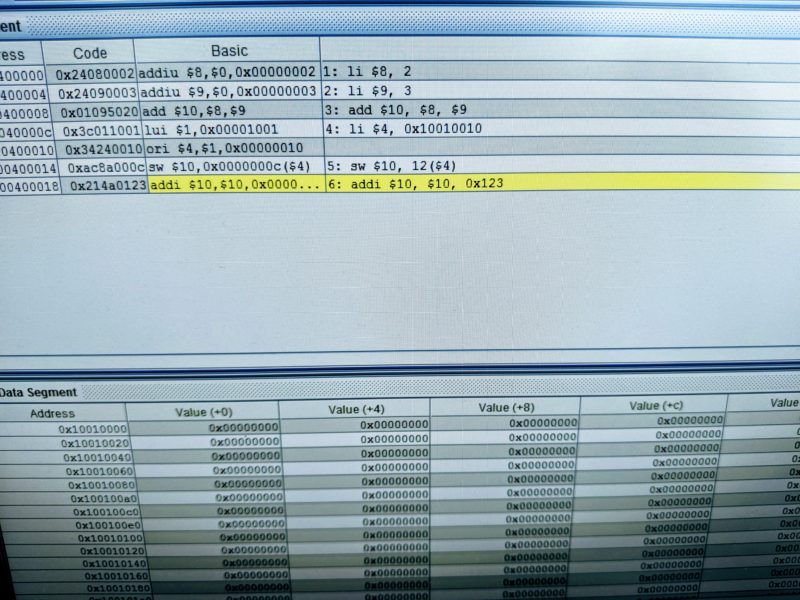

18.00-21.00. , . .

وسيستند في اليوم الثالث على تجربة برنامج تعليمي على معالجات من ستانيسلاف Zhelnio و الكسندر رومانوف . فقط قبل أن يطوروا ويستخدموا معالج التعلم schoolMIPS ، والآن سنستخدم schoolRISCV. إن بنية RISC-V تشبه إلى حد بعيد MIPS وبنيات RISC الأخرى (SPARC و ARM و POWER وما إلى ذلك) ، ولكنها خالية من عكازاتها ، والتي تكون منطقية في المعالجات البسيطة ، ولكنها تتداخل مع المعالجات المعقدة (تسجيل النوافذ في SPARC ، والتي لا معنى لها في البرامج مع كومة كبيرة ؛ فتحات تأخير الفروع في MIPS حتى Rev6 ، وهي جيدة على خط أنابيب ثابت بسيط مع إحضار تسلسلي للتعليمات ، ولكنها تتحول إلى صداع في خط أنابيب ديناميكي ، وما إلى ذلك).

نظرًا لوجود ما لا يقل عن ثلاث شركات في روسيا تصمم معالجات على بنية RISC-V ، وهذا مرشح جيد لمعالج روسي متطور مستقبلي وربما حتى معالج سطح مكتب وخادم ، وبما أن RISC-V يحل محل MIPS بثقة. خيول للتجارب المعمارية والمعمارية الدقيقة في جامعات العالم ، فمن الأفضل تعليم تلاميذ المدارس عليها.

17 . .

— , ..., . .. (), « » ( ).

15.00-15.15. -: ENIAC , IBM/360 Cray-1 Intel, ARM RISC-V: , .

.

15.15-16.30. : . RISC-V .

, - .

16.30-17.30. : . schoolRISCV, . .

, IVA Technologies.

17.30-17.30. . .

.

17.30-18.00. محاضرة ختامية: الخطوات التالية في إتقان تصميم الدوائر الرقمية وتطبيق هذه المعرفة على مسرعات حوسبة الذكاء الاصطناعي والتصميم المدمج.

الكسندر يوريفيتش رومانوف.

18.00-21.00. تمارين إضافية ومشاريع فردية للطلاب لتغيير المعالج ودمجه مع الأجهزة الطرفية. بمساعدة طلاب البكالوريوس والدراسات العليا في مجال الإلكترونيات الدقيقة من الجامعات المشاركة.

هنا ستانيسلاف زيلنيو يقوم بتدريس تلاميذ المدارس الصيف الماضي في زيلينوجراد:

نراكم في ندوة في ChipEXPO الافتراضية في سكولكوفو! سنحاول إقامة جزء من الحدث هناك والعيش بمساعدة معلمين من MIET و HSE MIEM و MIPT ، ولكن إذا لم يسمح الفيروس بذلك ، فسنقوم بإجراء ذلك بطريقة موزعة.